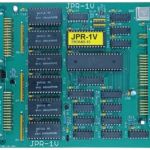

Deska JPR-1V je procesorová deska na bázi procesoru Z80, a je vylepšenou přímou náhradou původní JPR-1Z. Deska má tyto parametry:

- 100% kompatibilní s JPR-1Z

- určena pro operační systém CP/M

- procesor Z80

- frekvence sběrnice 2MHz, frekvence CPU 2/4MHz

- zkrácený RESET pro součinnost s DRAM

- vlastní odpojitelná BOOT ROM (2x 2kB)

- tři standardní vstupní a tři výstupní brány (mapování IO na adresách 1, 2 a 3)

- pin 22 konektoru K2 připraven pro klávesnice Consul (+5V)

- všechny výstupní signály CPU zesíleny budiči

- opravena chyba generování signálu STSTB pro mapování paměti

Tato deska byla spolu s deskami AND-1V, DGD-1V a RAM-1V zkoušena na nové „palcové“ sběrnici ARB-1 ImBUS9 na frekvenci CPU 10MHz (sběrnice 5MHz) s dlouhodobě stabilním chodem. Standardní desky systému SAPI však na tuto frekvenci nejsou projektovány, zejména ty s periferními obvody 8251, 8253, 8255, 8271, 8272 apod.

Deska generuje standardní frekvenci sběrnice 2MHz, kterou lze však zvýšit až na zmíněných 5MHz. Frekvence CPU se pomocí JUMPERu na desce volí buď stejná jako frekvence sběrnice, nebo jako její dvojnásobek. Přepnutí frekvence CPU lze provádět za chodu programu.

Vestavěná paměť BOOT ROM o kapacitě 8kB využívá pouze dvě banky 2kB se dvěma alternativními zavaděči, rovněž přepínatelnými pomocí JUMPERu na desce.

Oba konfigurační JUMPERy na desce je možno vyvést na tlačítka na ovládacím panelu.

Po restartu systému je VŽDY spuštěna zvolená varianta interní BOOT ROM na adresách 0000h – 07FFh (2kB). Zbylých 62kB paměti může být přítomno na sběrnici. Zavaděč po zavedení systému provede zápis na port s adresou 00h, čímž se odpojí BOOT ROM, a deska tak může adresovat plných 64kB na sběrnici. Během režimu BOOT je potlačeno čtení paměti ze sběrnice v adresním rozsahu 0000h-07FFh (čte se z interní BOOT ROM), zatímco zápis je do této oblasti povolen. Čtení a zápis v adresním rozsahu 0800h – FFFFh není v žádném režimu desky omezen. Systém mapování paměti pomocí signálů MAP1/MAP2 nemá vliv na volbu a funkci BOOT ROM. Během režimu BOOT svítí červená LED. Její zhasnutí indikuje ukončení režimu BOOT a přechod na plnou adresaci paměti na sběrnici, většinou to rovněž znamená start cílového systému.

Soubory ke stažení

- Popis JPR-1V rev. 1.1

Dosažený limit frekvence CPU o hodnotě 10MHz je dán nastavenou délkou signálu STSTB na 100ns. Zkrácením délky signálu STSTB na desce JPR-1V na hodnotu nižší (neměl by být problém jít na cca 60ns) lze zvětšit limit pro další pokusy s taktováním CPU, kdy lze použít 20MHz verzi Z80 v pouzdru DIL40. Pro 10MHz frekvenci CPU je nutné vyměnit oscilátor za typ s frekvencí 20MHz, frekvence sběrnice je pak 5MHz.