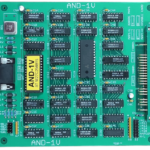

Deska AND-1V rev. 2.3 je textovou grafickou kartou systému SAPI-1 s výstupem na VGA monitor a je přímou náhradou originální desky AND-1Z. Deska má tyto parametry:

- 100% kompatibilní s AND-1Z

- textový formát 64×20 znaků

- formát znaku 10×24 pixelů

- volitelná pozice v adresním prostoru CPU s krokem 2kB

- možnost stránkování systémovým signálem sběrnice MAP1

- volba barvy monochromatického výstupu (1 z 15 barev inkoustu na černém pozadí)

- výstupní signál v normě VGA 640×480/60Hz

- čtení i zápis CPU je synchronní s časováním karty (nedochází k efektu „sněžení“ při přístupu CPU na kartu)

Historie

Karta prošla postupným vývojem, starší generace rev. 1.x je pro srovnání popsána zde. Jednotlivé revize přinesly následující změny:

- rev. 1.0 – testovací prototyp (znaky 6×12, fyzické rozlišení 384×480)

- rev. 1.1 – první finální verze (problémy se stabilitou při doporučeném blokování)

- rev. 1.2 – finální verze (bez návrhových chyb, na LCD nežádoucí resampling)

- rev. 2.0 – testovací prototyp (znaky 10×12, fyzické rozlišení 640×480)

- rev. 2.1 – první finální verze

- rev. 2.2 – podpora pamětí 27C256

- rev. 2.3 – začištěná finální verze, upraven potisk

Číslo revize a k ní přiřazené označení plošného spoje je vytištěno na plošném spoji ze strany spojů a je uvedeno i ve schématu. Rev. 1x a rev. 2.x jsou realizovány obvodově naprosto odlišně, nicméně v rámci revize 1.x jsou odchylky spíše minimální, stejně tak i v rámci rev. 2.x.

Soubory ke stažení

Galerie obrázků

Tato deska (spolu s DGD-1V) má na výstupu na datovou sběrnici obvod 74LS374. Ten má srovnatelné výstupní proudy s deskou JPR-1/JPR-1A a splňuje rovněž požadavky na výstupní proudy dle specifikace sběrnice S100.

Pokud by někdo potřeboval do své konkrétní sestavy vyšší výstupní proudy, lze se poohlédnout po obvodech 74S374, 74ABT374 apod.

Na Aukru, a asi i někde jinde, koluje napodobenina této desky pod jménem SAPI-1, VGA zobrazovač AND-1V23. Je nabízen o několik desítek Kč dráž než originál. Tak snad dotyčný „autor“ nenadělal v zapojení chyby, protože deska je mírně pozměněna. Na druhou stranu je možné, že některé mé chyby opravil :)

U desek AND-1V a DGD-1V je možné použít obvod 74S74 namísto 74LS74 na pozici generátoru signálu RDY. Proudové zatížení v log. 0 se tím zvedne z 8mA na 20mA, což umožní použít „tvrdé“ Theveninovo impedanční přizpůsobení na sběrnici.